﹥ 如您有興趣取得相關資料,請與我們聯繫

中科院龍園創新育成中心 W48館第二會議室

(桃園縣龍潭鄉龍源路134巷566號)

知名EDA大廠-新思科技(Synopsys),日前推出中階且支援Altera 之單一FPGA原型化開發板- HAPS-A31。HAPS-A31系統是第一個採用 Altera FPGA及 PCIe格式的HAPS開發板,並且提供與 Synopsys Synplify DSP 作系統驗證的功能。

思渤科技為Synopsys於台灣地區負責政府與教育市場的合作夥伴,本次我們特別邀請美國Synopsys原廠High Level Synthesis and System-Level 產品部行銷經理 Chris Eddington 來台灣,為設計者講解HAPS-A31與Synplify DSP最新技術與功能說明。並現場協助您解答工作及研究時曾碰到關於Synopsys產品使用上的各種疑難雜症。歡迎踴躍報名參加!

.jpg)

![]()

Synplify DSP-高效能DSP方案

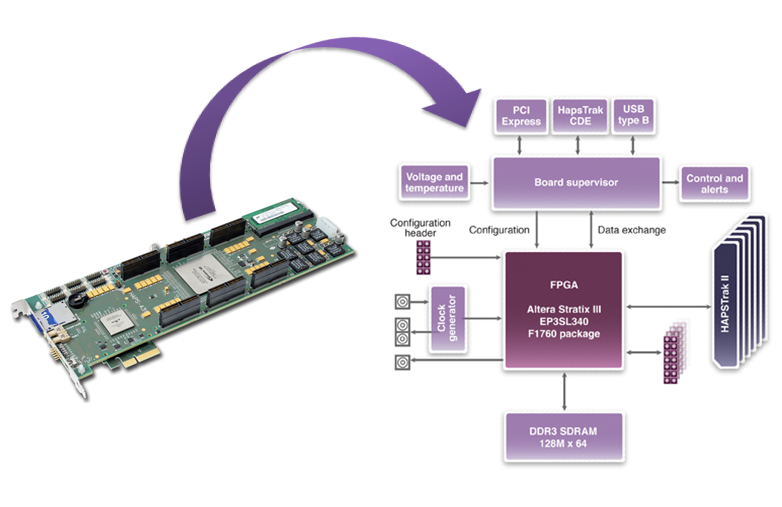

Synplify DSP 擁有多樣DSP資料庫,可以利用基於模型的方式(Model-based Design)作演算法開發。傳統的設計方法是撰寫硬體描述語言來完成演算法的設計跟實現,撰寫程式及測試程式並利用硬體模擬器(Hardware Simulator)來做模擬,這種方式其實浪費許多工程師的人力及時間。基於模型的設計就是先利用Synplify DSP的資料庫建立硬體演算法模型,在MATLAB與Simulink平臺,進行演算法開發,並可與不同領域的資料庫(Blocksets)進行系統測試與模擬,利用Synplify DSP 引擎介面可以將硬體模型自動產生Verilog 和VHDL RTL的程式碼及測試程式,此介面奕提供架構上的最佳化選項 ,可對整個系統架構做最佳化。

Synplify DSP 擁有多樣DSP資料庫,可以利用基於模型的方式(Model-based Design)作演算法開發。傳統的設計方法是撰寫硬體描述語言來完成演算法的設計跟實現,撰寫程式及測試程式並利用硬體模擬器(Hardware Simulator)來做模擬,這種方式其實浪費許多工程師的人力及時間。基於模型的設計就是先利用Synplify DSP的資料庫建立硬體演算法模型,在MATLAB與Simulink平臺,進行演算法開發,並可與不同領域的資料庫(Blocksets)進行系統測試與模擬,利用Synplify DSP 引擎介面可以將硬體模型自動產生Verilog 和VHDL RTL的程式碼及測試程式,此介面奕提供架構上的最佳化選項 ,可對整個系統架構做最佳化。

在MATLAB與Simulink平臺上,設計人員能儘早在上面模擬整個系統,能快速驗證演算法的程式發現並解決問題,自動產生程式碼的動作也讓你省去寫程式及測試程式的動作。Synplify DSP 的好處如下:

- 從DSP 演算法到硬體整合更加容易

- ASIC的快速原型化設計工程

- 更可靠的設計及驗證方式

- 模型可以提供重複性和便利性

- 增加總生產力,縮短開發時間

HAPS-A31展示—支援Altera和採取PCIe格式之中階HAPS開發板

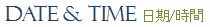

HAPS-A31 系統是新思提供單一FPGA原型化開發板,配備有Stratix III SL340 FPGA (擁有兩百萬個 ASIC Gate 及 576 個內建的18x18-bit的硬體乘法器17Mbits 的內部記憶體)及一個1 GByte DDR3 SDRAM SO-DIMM 模組。

HAPS-A31系統是第一塊包含 Altera FPGA 的HAPS開發板及第一個採取 PCIe 格式的HAPS板子,並提供與 Synopsys Synplify DSP 作系統驗證的功能。PCIe 的介面可以讓您插入任何4-lane PCIe slot,亦可擴充客制化的周邊到 6 HapsTrak II 連接器(714 I/Os) 及signaling rates up 1 Gbps LVDS 及600 Mbps single-ended。板子上提供六個I/O 電壓區域可以調整為2.5、1.8、1.5 或1.2 V ,燒錄的方式可由JTAG cable、SD card、HapsTrak CDE來配置(下載 HAPS-A31 型錄)。

On-board functions of the HAPS-A31 board

-

Synplify DSP 的優勢

-

Synplify DSP 提供讀資料庫範圍

-

影像處理及電信方面的應用範例

-

Synplify DSP與HAPS-A31的連結

-

HAPS-A31 演示

![]()

本場次為:中科院場

請登入會員並點選本網頁上下方「報名此活動」直接進行網路報名即可。

任何疑問,請於09:00~17:30 來電 (03) 6118668#366/369 ,或 mail 至 mkt@cybernet-ap.com.tw 查詢

﹥ 如您有興趣取得相關資料,請與我們聯繫